성균관대학교 전자전기공학부 유우종 교수 공동 연구팀, 분자 한 개, 세상에서 가장 작은 메모리 개발

작성자 정보

- 작성일

컨텐츠 정보

- 1,296 조회

- 0 추천

- 목록

본문

성균관대학교 전자전기공학부 유우종 교수 공동 연구팀이 분자 한 개로 동작하는 세상에서 가장 작은 메모리를 제작하고 이를 집적화시키는 기술을 개발했다. 유우종 교수는 화학과 이효영 교수, 에너지과학과 두옹딘록 교수와 함께 연구한 이같은 내용을 과학기술 분야 국제학술지 ‘네이쳐 커뮤니케이션’(IF: 17.69)에 발표했다.

메모리 반도체 크기가 작을수록 반도체 칩에 더 많은 메모리를 넣을 수 있다. 기술력이 가장 앞선다고 평가받는 삼성전자가 양산 중인 14nm D램 메모리가 현재 가장 작은 크기이나, D램은 공정 난도가 높아 선폭 1㎚(10억분의 1m)를 좁히는 데도 2~3년이 걸리는 등 기술적인 어려움이 많다. 차세대 반도체 소자 후보인‘분자전자소자(molecular electronics)’는 나노미터 크기의 매우 작은 분자를 조합해 전자소자의 핵심 구성요소로 사용하는 것으로, 메모리 미세화의 어려움을 극복할 기술로 관심받고 있다.

기존에는 분자전자소자를 제작하기 위해 나노미터 크기의 미세간극을 가진 전극을 만든 다음 그 틈에 분자 한 개를 넣는 방식을 사용하였다. 그러나 이러한 미세간극 전극을 만들기 위해서는 기존 반도체 공정 기술을 사용하기 때문에 D램 미세공정과 동일한 기술적 한계를 보였다.

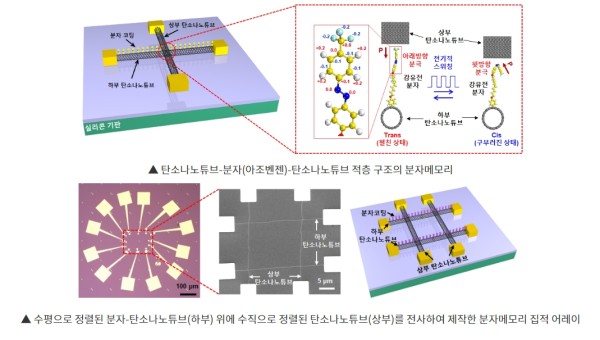

이를 해결하기 위해 유우종 교수 연구팀은 분자가 일렬로 코팅(자가조립) 된 매우 가는 전선(직경 1nm)인 탄소나노튜브(하단) 위에 탄소나노튜브(상단)를 교차로 적층한 구조를 제안했다. 탄소나노튜브가 교차하는 지점에는 자가조립 된 분자 한 개가 상, 하부 탄소나노튜브 전선 사이에 위치하여 분자전자소자를 구성한다. 이렇게 제작된 분자 메모리의 크기는 탄소나노튜브 교차 면적인 1nm2로 현재 생산되고 있는 가장 작은 D램 메모리(14nm)보다 14배 작다.

이번 연구에서는 나노미터 크기의 초미세 분자전자소자를 만들기 위해 첨단 반도체 공정 대신 매우 간단하고 저렴한 전사기법을 사용하였다. 마치 레고 블럭을 쌓아 올리듯 분자로 코팅된 탄소나노튜브(하단) 위에 탄소나노튜브(상단)를 얹어 올려놓는 방식이다. 탄소나노튜브(상단)가 탄소나노튜브(하단)의 분자 코팅 위에 놓이고, 교차점에 자연스럽게 분자 길이만큼의 전극 간격이 형성된다.

전사기법은 분자메모리의 집적화에도 매우 유리하다. 미세간극 전극을 개별적으로 제작해야하는 기존의 분자전자소자와 달리, 수평으로 정렬된 분자-탄소나노튜브(하단) 위에 수직으로 정렬된 탄소나노튜브(상단)를 간단히 배치하는 것만으로 집적어레이를 제작할 수 있다. 이렇게 제작된 분자메모리는 모두 완벽한 메모리 동작(수율 100%)을 보였다.

연구진은 이번 연구에서 사용된 아조벤젠(azobenzene) 분자의 강유전성을 처음 확인하였다. 아조벤젠은 외부에서 전압을 인가하면 분자의 꼬리 부분(CF3 group)의 구조가 펼친 상태(Trans)와 구부려진 상태(Cis)로 바뀌는 특성이 있다. 연구진은 이론물리적 시뮬레이션을 통해 아조벤젠의 꼬리가 전기적으로 분극되어 있고, 펼친 상태와 구부려진 상태를 전환할 때 분극의 방향이 바뀌는 강유전체 특성을 나타내는 것을 확인하였다. 탄소나노튜브-분자-탄소나노튜브 구조에서 탄소나노튜브 전극과 분자 사이에 형성되는 쇼트키 장벽(Schottky barrier)은 분자의 강유전성 분극 방향에 따라 크기가 달라지며 전류량을 변화시킨다. 이 전류량 차이는 1과 0을 구별하는 메모리로 사용된다. 외부 전압이 차단된 후에도 강유전체의 분극 방향이 일정하게 유지되어 전류를 공급하지 않고 데이터를 유지하는 비휘발성 메모리 특성을 보였다.

유우종 교수는 “본 연구에서는 고가의 최첨단 반도체 공정 대신 쉽고 저렴한 전사기법을 사용하여 분자 메모리를 현재 D램 메모리보다 14배 작게 만들었으며, ‘초미세 반도체 = 비싸고 어렵다’는 공식을 깨뜨렸다”며“이 기술은 향후 국내 반도체 초격차를 이어갈 주요 기술이 될 것으로 기대된다.”고 밝혔다.

※ 논문명: CNT-molecule-CNT (1D-0D-1D) van der Waals integration ferroelectric memory with 1-nm2 junction area

(저널: Nature Communications, https://www.nature.com/articles/s41467-022-32173-8)

관련자료

-

링크